To combat the risk of sub-standard or counterfeit semiconductors entering critical supply chains, tighter purchasing controls are designed to exclude or segregate all bare die products presented without the required certified paperwork.

However, similar to encapsulated (packaged) semiconductors, circumstances arise where there is a need to use bare die which lack some or all of the necessary paperwork. These circumstances arise predominantly due to part scarcity or obsolescence, where without critical part availability, the economic, strategic and timing impact to make assembled end product and delivery of the larger program is significant.

Since encapsulated (packaged) components comprise >99% of all semiconductors supplied globally, there are already a multitude of test steps and standards relating to their assessment. However the bare die format itself is a much more specialist topic with unique considerations and where some of the criteria applied to packaged products do not apply.

The natural result is a hybrid process which combines some of the general criteria applied to packaged components plus specific criteria added for bare die.

We recommend and support a basic process flow similar to AS6081 but critically with additional edits and criteria specific to the bare die format.

It's important to understand that every situation is different and the sum of factors identified via incoming inspection and intended end use/customer confidence requirements ultimately dictate the test steps and sample sizes we recommend.

Minimum Inspection:

- Documentation - Incoming Paperwork, Packaging & Wafer Jar / Waffle Tray Label Inspection

- Quantify lot homogeneity

- Establish possible age/datecode

- Comparison with official documentation from the same manufacturer via cross-reference with our internal document archive

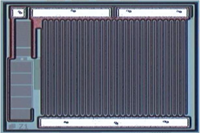

- External Visual Inspection - Die verification and assessment of visual quality

- General

- Catalogue geometry and die markings

- Cross-reference geometry against our official die geometry archive

- Dimensional measurement

- Visual assessment of top and back metal (if present)

- Detailed

- 100% visual quality inspection to MIL-STD-883 or MIL-STD-750 as applicable

- General

Additional Tests (as agreed between Customer and Die Devices):

- XRF (non-destructive) or EDS/EDX

- Scanning Electron Microscopy

- Quantitative Surface Analysis

- Wirebond Pull

- Die Shear

- Thermal Cycling Test

- Electrical Testing - DC, AC

- Burn-In (Pre & Post)

- Scanning Acoustic Microscopy (SAM)

Depending on the end use and how this bare die will be assembled, we may also recommend alternative flows which by default incorporate some of the testing and work detailed above.

For example, for die intended for use in military hybrid circuits we would recommend MIL-PRF-38534 Class H. For die intended for use in space hybrid circuits we would recommend MIL-PRF-38534 Class K

Why consider our validation flow?

- Our company has over 85 years combined experience in the bare die supply industry

- We hold an archive of official bare die information dating back to the early 1970s for inspection/verification/correlation purposes

- Bare die inspection, electrical test, burn-in, thermal cycling, bond pull, die shear and more is all performed in-house

- We routinely perform military and space level qualification flows on both certified and non-certified bare die products

-

Our inspection tools are world class, with 4K resolution, micron level measurement capability and 3D image stacking capability.

More information on specific test services is provided by our sister entity reltronix.com who share our capabilities and are also located at the same site.