Typical drivers

Critical functionality:

- No drop-in replacement with the same electrical function in the market

- The obsolete part interacts uniquely with other components on the board. This means a system level re-design changing more than just the obsolete part.

- Product re-design / re-qualification protocol + lead-times prevent deliverance of orders.

Diminishing Manufacturing Source and Material Shortages (DMSMS):

- Use of grey market inventory presents unacceptable risk

- Older material without provenance or proof of suitable storage presents unacceptable risk

- Exposure to multiple small lots means increased anti-counterfeit and screening procedures

- LTB (Last-time-buy) was not placed and the wafer fab process is closed down.

Footprint:

- For bare die users - The original die footprint was unique such that electrical alternatives are either wire-bonding compatible or don't fit on the substrate pad.

- For package users - The package footprint was unique, no die are supported or available after-market.

Economics:

- The volumes needed or budget dollars are not enough to engage a large semiconductor organization

- The cost of re-design or re-qualification is high

- Cost of known good inventory becomes increasingly prohibitive

- Cost and volume of after-market material screening becomes increasingly prohibitive.

Benefits

Technical:

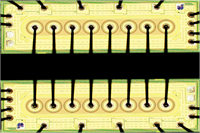

- Die size is tailored to be a mechanical match with the original component

- Bonding pad locations are tailored to the original component footprint for wire bonding compatibility

- Parameters are warranted against either original manufacturers datasheet or customer agreed specification.

Commercial:

- Flexibility on minimum production quantities and costing structure

- Significantly lower engagement cost compared with prime semiconductor companies

- Long term product support and availability.

Indicative lead-times to first silicon:

- Low to Medium complexity digital IC - E.g. Logic gate variant - Typically 14 Wks

- Lower to Medium complexity analog / linear - E.g. Legacy amplifier - Typically 14-16 WKs

- Lower to Medium complexity mixed signal IC - E.g. Slope modulator / demodulator - 24 Wks

- Medium to High complexity Digital IC - 48 Wks

- Medium to High complexity Analog IC - 48 Wks

Lead-times vary based on component technology.

Firm lead-times are given during the evaluation / quotation process.

Typical Process

The process is broken into four main stages, evaluation, quotation, development and qualification.

PLEASE NOTE - ALL COMPONENTS MUST BE CONFIRMED OBSOLETE FOR US TO ENGAGE

1) Evaluation

Review original datasheet and die topology (if available)

Confirm end use, customer diligence, technology export compliance

Obtain samples - Either package or bare die can be used

Check IC for patented IP before proceeding further. Patented IP criteria are below.

Either:

- The original IC contains patent IP essential to the end function then a license must be sought from the original maker. No license = No development

- The original IC contains patent IP but the same end function can be achieved using our own alternative technology. The original patent IP is not used.

- There is no patent IP present.

Discuss die qualification / specification requirements - E.g. Mil-STD 883 Class H / Class K or other standards.

Confirm any parameter behavior required outside of standard datasheet.

2) Quotation

If all above checks are compliant:

- Provide price - MOQ (Minimum order qty) basis upward with price breaks.

- Provide lead-time - To first silicon + qualification time

- Please note - Depending on complexity and development time a stage payment structure may be required.

3) Development cycle

Development of schematic diagram

Technology choice

SPICE parameters and simulation modeling

Develop wafer probe test schedule and test tooling

Wafer fab - The part may require multiple test + design revision cycles before release of first silicon

Release first silicon

4) Qualification

Wafer dicing & inspection

Qualification sample assembly

Qualification test flow

Customer also has the option to receive first silicon ahead of any qualification plan where required.

Supported Technologies

Bipolar

CMOS

BCDMOS

Feature sizes from 1.5µm to 65nm

How to investigate further?

A budgetary costing and leadtime can be provided after analysis of the original component datasheet. An available copy of the bare die layout or geometry is also useful to the process but not essential. If the budgetary returned is in the right area then further analysis of mechanical samples takes place in order to provide a firm formal quote. Where no mechanical die samples are available then a sample can be extracted from packaged parts.

For assistance with bare die re-engineering please contact sales@diedevices.com