SiP - System-In-Package

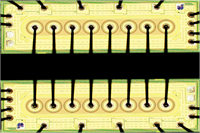

Multiple bare die are assembled into a single plastic package, usually a die stack. The bare die used typically span different technology genres and provide a fully integrated suite of functionality or system.

Key benefits:

- Form factor

- Performance

- Power consumption

Bare die integration via SiP provides a possible solution when the system functionality can't be achieved either monolithically (System-On-Chip) or by a single chip system due to development time, size constraint, technology limitation or commercial cost.

SiP Versus SoC (System-On-Chip)

SoC pros:

- Smallest possible form factor

- Likely best electrical performance

- Lower assembly complexity / production costs.

SoC cons:

- Costs not reducing further at smaller feature sizes <65nm

- Long development time and high NRE costs

- Risk of failure / additional re-spin costs.

SiP pros:

- Rapid and lowest cost development cycles (subject to bare die availability)

- MOQs becoming economical for low to medium volumes (subject to bare die availability)

- Maturing eco-system for developing multi-die ICs - Driven further by IoT and RF integration.

SiP cons:

- Not all bare die are easily available for low qty prototyping or low qty production

- Any change in component die topologies or sizes may mean change to the package design.

SiP Versus single-chip layout

SiP pros

- Much smaller form factor

- Reduced power dissipation by 3-10X

- Speed increase due to shorter path lengths

SiP cons

- Requires ease of access to all bare die in the system

- Commercial Die MOQ may not be compatible with the project volume

- Requires specialist knowledge of SiP design and modeling - thermal and parasitics

- Assembly process needs more control due to reduced i/o pitches.

SiP Benefits in summary

SiP creates a form factor which is very similar to SoC or ASIC in X-Y profile. Whilst not as electrically efficient as a bespoke SoC or ASIC design it does provide a much enhanced performance than a single chip system layout.

The SiP industry is increasing and forecast to accelerate faster. The SiP industry is being driven by Sensor fusion, MEMs integration, IoT applications and Automotive applications which require a design-to-market agility and technology mix that ASIC or SoC cannot accomplish easily with the right cost or timescale. Therefore the ease of support and availability of bare die for SiP integration is key.